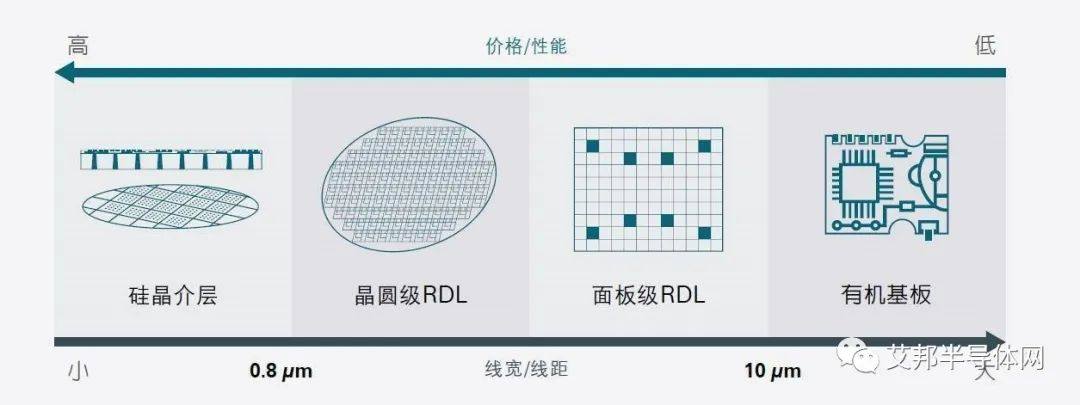

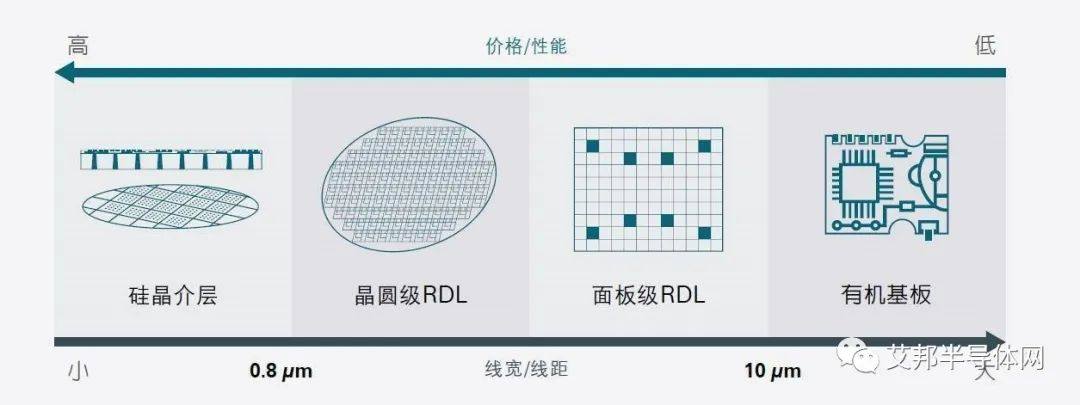

大家都知道整个封装界的升维之路上:从2D封装到2.5D再到3D封装(备注:各种封装形式差异可参看艾邦半导体公众号)。Chiplet级的封装如果以载体的形式来分则分为两种:晶圆级封装(Wafer level package, WLP)和面板级封装(Panel level package, PLP)。根据载体的材料来分可以归为三类:有机物基板、硅基板、玻璃基板。特别申明:本文封装特指扇出型封装。

在阅读本文之前,欢迎识别二维码申请加入半导体封装产业链微信群

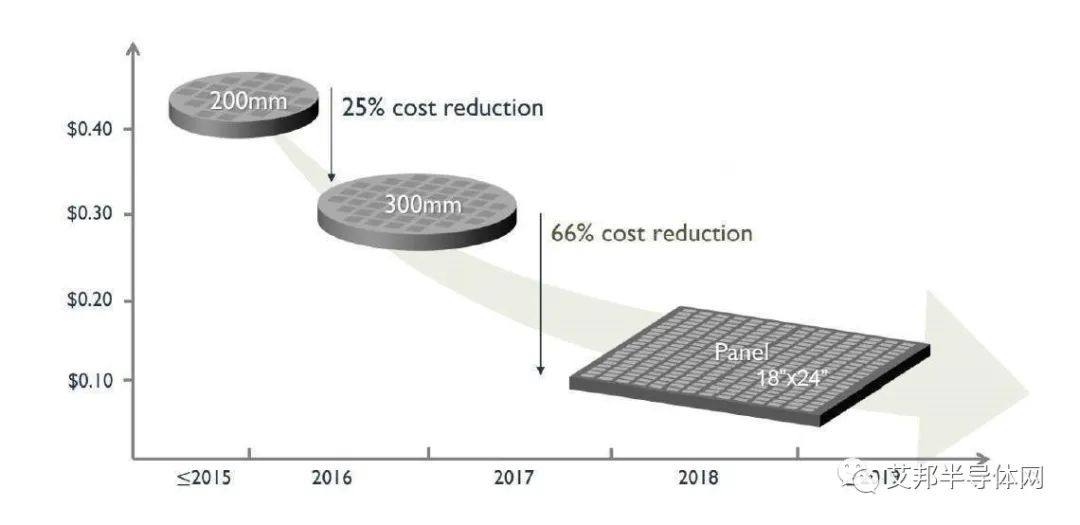

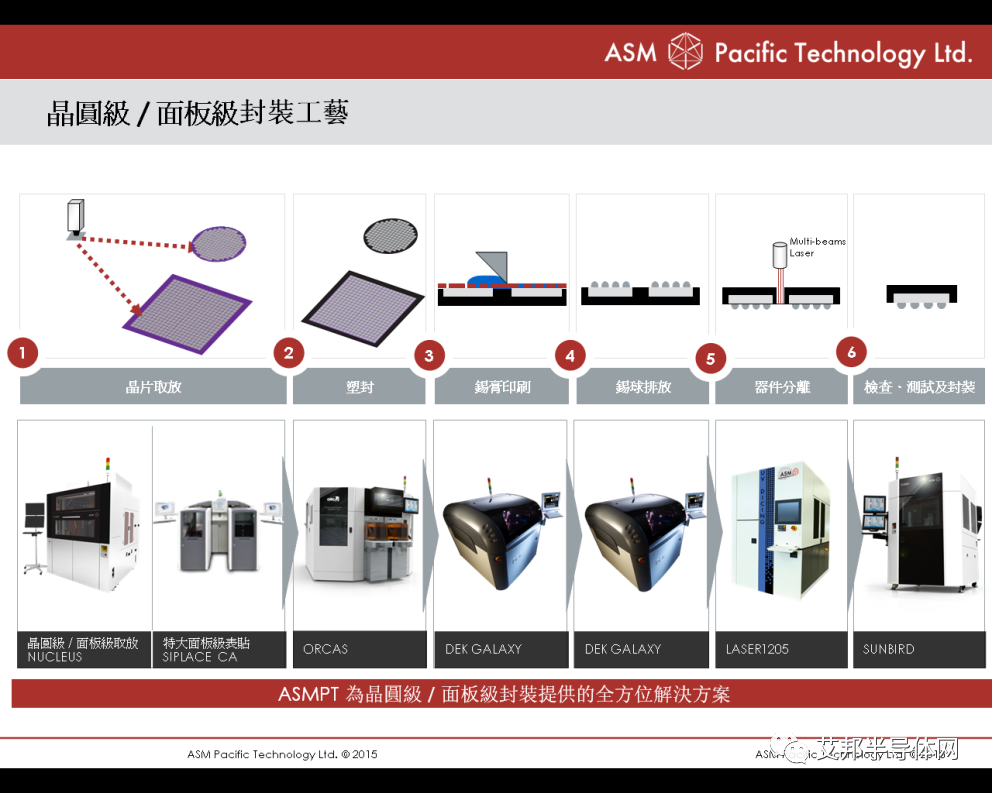

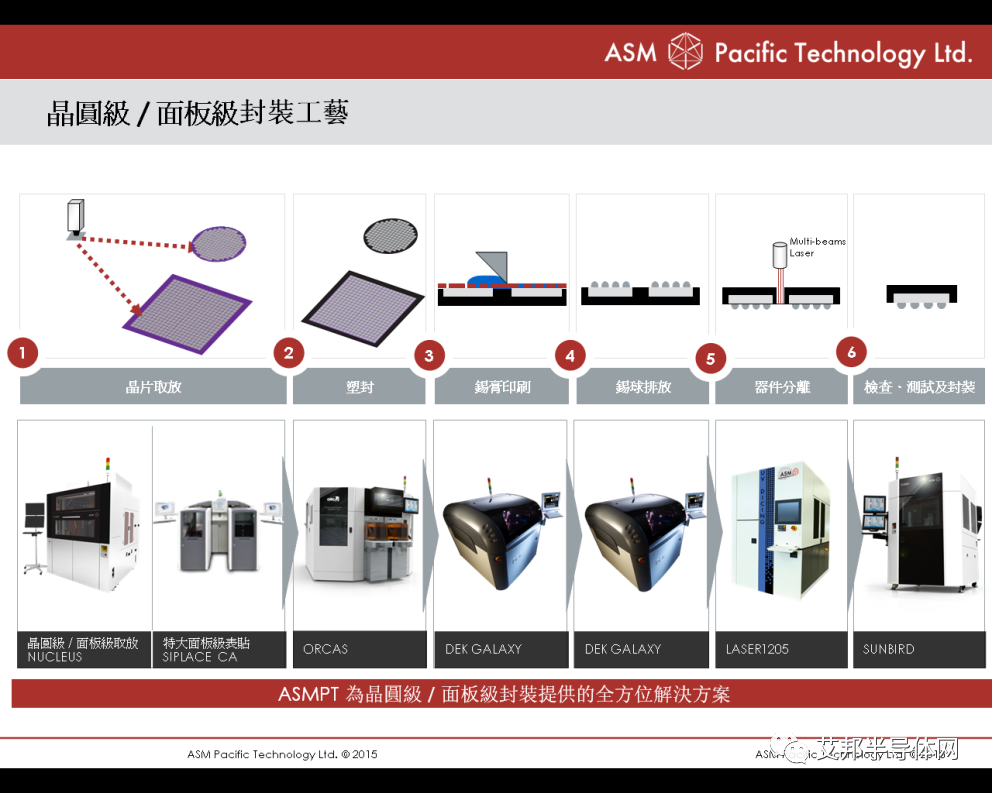

面板级封装的优势主要在于成本。我们将300mm晶圆级封装与515x510mm面板级封装相比,可以看到如图2所示,面板级封装芯片占用面积比高到93%,而晶圆级封装则只有64%。这几何级别的差异,直接导致生产过程中生产速率UPH的巨大差异。另外,根据Yole 报告,例如FOWLP技术面积使用率<85%,FOPLP面积使用率>95%,可以放置更多的芯片数,成本也比FOWLP便宜。具体推算从200mm过渡到300mm大约能节省25%的成本,从300mm过渡到板级,则能节约66%的成本。面板级封装的成本与晶圆级封装相比将会降低66%。面板级封装工艺流程与晶圆级封装本身没有太大差异。但是由于载体不同,需要独立开发生产设备及相应系统。下面简单介绍一下当前设备供应商对面板级封装的开发情况:在面板级封装光刻机领域,日本佳能动作非常快,佳能在错失超紫外光刻机的机遇后,不会再放过任何一个机会。如图4所示,佳能在2020年7月推出型号为FPA-8000iW的光刻机,具备对应尺寸最大到515×510mm大型方形基板的能力以及1.0微米3的高解像力。在面板级封装RDL工艺领域,Manz是领跑者之一,2016年Manz开始进军半导体先进封装领域,2017年研发并售出第一台用于半导体先进封装FOPLP的湿法化学设备,并于2019年交付首条半导体板级封装全自动RDL生产线,面板尺寸也从515mm x 510mm开始,演进至600mm x 600mm,直至2022年升级至业界最大的700mm x 700mm面板,并克服了面板翘曲问题,见图5。Manz生产设备已出货全球知名半导体制造商,应用于车载与射频芯片的封装量产。Manz新一代面板级封装 RDL生产线,在制程上接续干膜制程,完成线路成型,其均匀性以及填孔能力分别表现在线宽线距可至 ≥10μm及盲孔孔径≥25μm;图5 Manz集团亚洲区总经理 林峻生先生展示以Manz新一代面板级封装 RDL自动化生产线所试制之产品 在面板级晶粒贴装领域,ASMPT,华封等都有相应产品。其相关产品根据UPH不同都可以达到2.5~7微米精度。基本可以满足大多数封装产品的需求。

在代工领域,国际上仅有Powertech和三星等大厂有量产的面板级封装产品。特别注意的是国内成都奕斯伟,也布局Fan out板级封测系统集成电路服务及系统解决方案。该项目于2021年开工,预计2023年正式投产。项目具有扇出型、高密度与高带宽、面板级封装三大技术优势。这家公司由“面板显示之父”、前京东方董事长王东升领衔,也特别符合近几年的主流即显示面板商向半导体面板级封装方向探索的大思路。一、设备供应商没有统一规范,面板尺寸没有通用标准,比如当前主流的是515mm x 510mm和600mm x 600mm,也有510mm x 415mm。二、当前需求量还较低,设备供应商没有特别高的热情来冒险开发整条产线。

三、初期产品还仅限于低密度产品,并没有发挥出面板级封装的低成本优势。

四、业界希望面板级封装芯粒与芯粒间的间距可以达到2微米,而当前量产的产品其晶粒与晶粒间的间距最低可以达到5微米。

五、面板级封装还需要开发特殊的检测及测量工具。

六、面板级封装与当前晶圆级封装数据系统不完全兼容,还需进行一定的改造。这也是为什么大厂台积电至今也没有意向开发面板级封装。英特尔虽然也尝试面板级封装但是没有用于fan out。总之,面板级封装技术被广泛使用仍需时日,需要大量的前期投资来打造完整的产业生态链。1.https://baijiahao.baidu.com/s?id=1670269168270249241&wfr=spider&for=pc2.https://www.eet-china.com/news/202212137784.html3.https://www.manz.com/cn/company/news/manz-45/4.https://semiengineering.com/planning-for-panel-level-fan-out/原文始发于微信公众号(艾邦半导体网):先进封装之面板级封装(Panel Level Package,PLP)