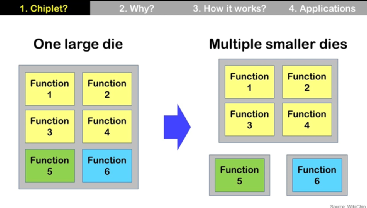

大家好,欢迎来到半导体内容。我接到一个讲讲关于Chiplet的请求,所以今天的话题是Chiplet。我们来谈谈吧。Chiplet是一种半导体技术,使用多种小芯粒来实现目标功能,将原本应该由一个芯粒来完成的任务,分为多种较小的芯粒集成在一起来实现。从而,减少产品开发时间和成本。Chiplet不是指封装类型,它是封装架构的一部分。通过chiplet,多种芯粒可以集成到现有的封装类型中,例如2.5D、3D、扇出及多芯片模块。

观看视频

想象一下,我们有一个大芯片,它有CPU,GPU,RAM及其它功能块都在一个芯片中作为SOC系统芯片。但这是非常昂贵的,并且有许多挑战使这些产品很难量产。幸运的是,我们可以通过多种较小的芯粒来实现所有这些功能,而且这样在成本上更合理。但是由于我们需要在每个芯粒上添加接口模块,所以总的所有芯粒总面积将超过全部集成在一个芯片上。这是chiplet的一个简单概念。因此,Chiplet是大型系统集成芯片的良好解决方案,通常用于高性能计算,而不是智能手机中的小芯片。一种使用先进的半导体制程如45nm、16nm甚至7nm。

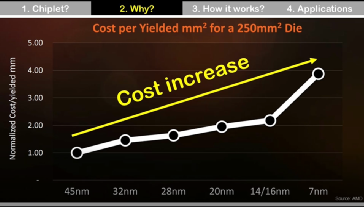

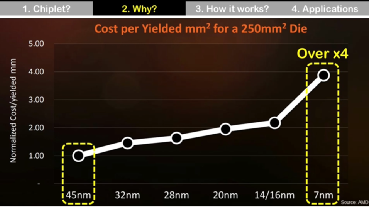

随着大芯粒的成本继续增加。针对一个250mm²尺寸的芯粒,14或16纳米制程的成本是相同尺寸的45纳米芯片的2倍以上。而7纳米芯片比45纳米芯片贵4倍以上。而到我们最近谈论的5纳米甚至3纳米,成本更将不断增加。这意味着使用先进制程制造大型SoC芯片正在失去其经济效益。这就是为什么这个行业又开始使用chiplet了。

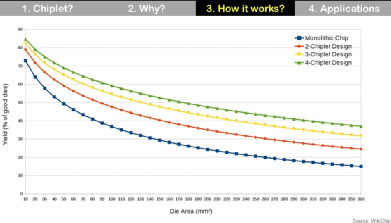

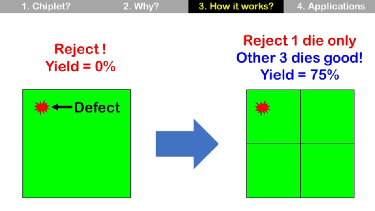

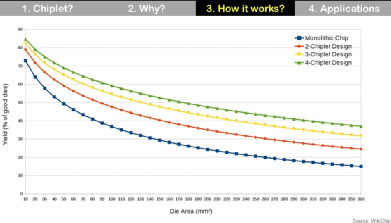

Chiplet是将大型的单一芯粒分解成多个较小的芯粒。它是如何工作的?这是一个大芯粒和4个小芯粒之间的简单比较。如果在芯粒的左上角有缺陷,则整个芯粒就无法使用,所以良率是0。如果我们有4个小芯粒,并且在完全相同的位置存在相同的缺陷。然后4个芯粒只有一个不能使用,良率为75%。这意味着我们仍然可以节省3个芯粒。它也适用于边缘DIE。在左边,我们有大量无法使用的边缘DIE。在右边,我们也有相类似的损失,但较小的芯粒比较大的芯粒具有更高的良率。这是一个芯粒与chiplet 的有2,3或4个芯粒之间的比较。对于360mm²的一个芯粒,我们仅有15%的良率。但针对4个芯粒的chiplet 设计,良率将是前者的一倍以上。即使4个芯粒的chiplet 设计的总面积比一个大芯粒多出10%,Chiplet的设计明显提高了良率和合理性。

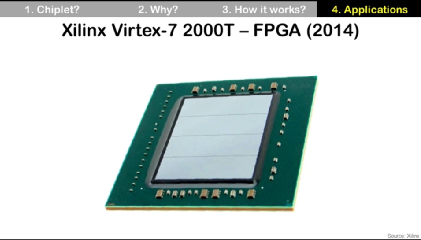

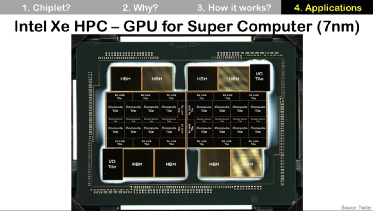

早在2014年,赛灵思生产的72000,它使用了4个较小的芯粒,而不是1个大芯片。这是AMD史诗级般的第二代封装,它是使用7nm的服务器CPU。其封装尺寸为58.5mm乘75.4mm,它非常大。中心有8个使用7nm技术的CPU和一个I/O 芯片使用14nm技术。这是英特尔XE HPC,它里面的GPU使用7nm技术,现在英特尔只在实验室中使用它。它有47个组件,包括2个基础芯片使用英特尔10nm技术。16个计算核心使用TSMC的7纳米技术。

11个缓冲使用英特尔十纳米技术,2 个I/O芯粒由代工厂代工。8个HBM存储器堆栈由存储厂加工。没有chiplet技术,是不可能将47个芯粒的功能一次性在单个芯片上加工完成的。尽管chiplet有很多好处,但它也有一些挑战。我们需要思考芯片到芯片的互连,芯片设计师和封装设计师的协同,多个小芯粒的测试也将非常不同于一个大芯粒的测试等。

观看视频

来源:youtube semicon talk

原文始发于微信公众号(艾邦半导体网):先进封装Chiplet 技术介绍(视频)