回顾过去五六十年,先进逻辑芯片性能基本按照摩尔定律来提升。提升的主要动力来自三极管数量的增加来实现,而单个三极管性能的提高对维护摩尔定律只是起到辅佐的作用。随着SOC的尺寸逐步逼近光罩孔极限尺寸(858mm2)以及制程的缩小也变得非常艰难且性价比遇到挑战, 多芯片封装技术来到了舞台的中心成为进一步提升芯片性能的关键。覆晶键合技术已然成为先进多芯片封装最重要的技术之一。尽管某些基于晶圆级或者面板级扇出型封装的工艺流程可以不用到覆晶封装,但是这个技术方向有其自己的应用局限性。比如其目前量产重布线层的层数大多在五层以内,使其不太适合服务器芯片的封装。如今最常见的基于焊球的覆晶键合封装技术一共有三种:回流焊(mass reflow), 热压键合(Thermo Compression Bonding or TCB)和激光辅助键合(Laser Assisted Bonding, or LAB)。基于铜铜直接键合的覆晶封装不在这个文章的讨论重点,我们会在后续的文章中讨论目前最具希望能进一步缩小的bump间距(bump pitch scaling down)的方法,比如混合键合(Hybrid bonding)和铜铜直接热压键合等等。

表一在high level总结了这三种基于焊球的覆晶键合封装技术的优缺点。 可以看到没有一种键合方式是完美的。对于某个产品来说,任务是要找到最合适的键合方法。作为本文的重点,热压键合最大的优势是对die和基板(可以是substrate, another die or wafer or panel)的更为精准的控制。

|

覆晶键合方法 |

回流焊 |

热压键合 |

激光辅助键合 |

|

优势 |

1.Throughput高 2. 加工成本相对低 3. 有自校正(self alignment) |

1. 有Die曲翘控制 2. 有基板曲翘控制 3. Chip gap variation小,且可调控 4. Bump pitch可以接近10um |

1. 有基板曲翘控制 2. 加工成本相对热压键合低 3. 有自校正(self alignment) 4. Throughput相对热压键合高 |

|

劣势 |

1. 无Die曲翘控制 2. 无基板曲翘控制 3. 通常留有因热力学效应产生的高应力 4. Bump pitch通常要求大于60um 5. Chip gap height variation大 |

1. Throughput低 2. 加工成本相对高 3. 通常无自校正(self alignment) |

1. 无Die曲翘控制 2. Bump pitch通常要求相对较大 3. Chip gap height variation大 |

表一:基于焊球的覆晶键合技术

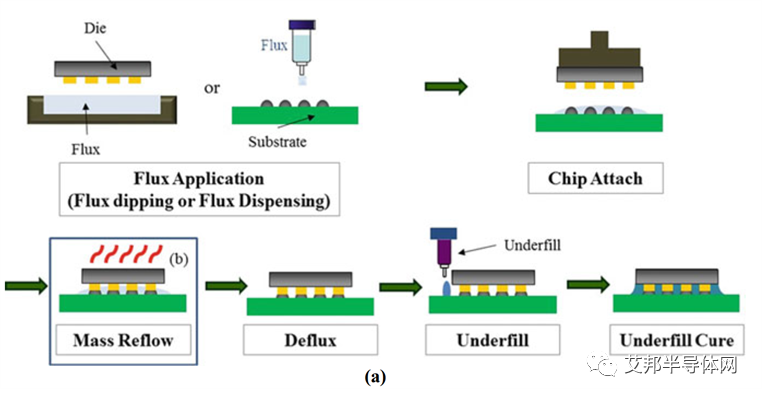

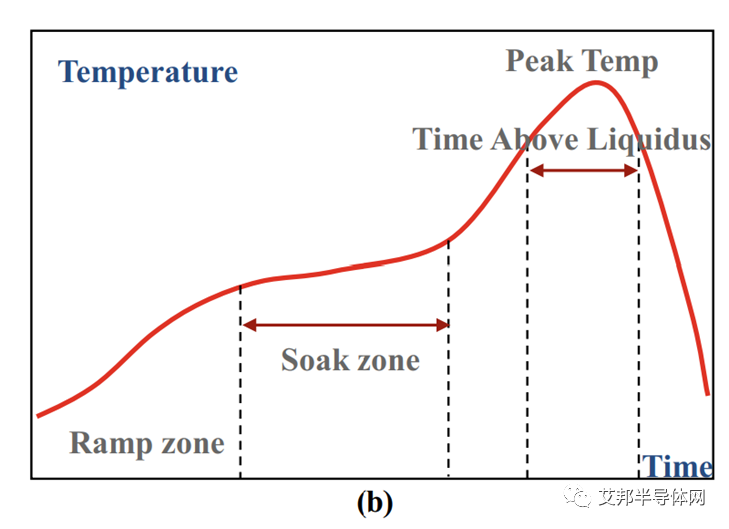

接下来我们着重讨论一下高端的逻辑芯片的键合方式为什么逐步从回流焊键合过渡到热压键合。我们会在另一篇文章里着重讨论激光辅助键合。图一(a)给出了一种常见的回流焊芯片键合流程。先将芯片上的bumps沾上助焊剂(flux)或者在基板上的C4 (controlled-collapse chip connection)区域喷上定量的助焊剂。然后用贴片设备将芯片相对比较精准地放到基板上。然后将芯片(die)和基板整体放到一个回流焊炉子里。常见的回流焊的温度控制由图一(b)给出。整个回流焊的时间通常在5到10分钟。虽然时间很长,但因为这是批量处理,一个回流焊炉同时可以容纳非常大量的加工产品。所以整体的吞吐量还是非常高的,通常可以达到每小时几千颗芯片的产量,或者更高。根据所使用的回流锡膏的种类,回流温度的峰值一般控制在240ºC到260ºC。在回流键合后通常我们需要去除助焊剂和加CUF (Capillary Underfill毛细管底部填充料)来填充bump之间的空隙来提供产品的可靠性。常见的回流焊过程中,我们不对芯片和基板做过多限制。这导致芯片和基板的曲翘得不到有效的控制,使得在芯片与基板之间的距离(chip gap height)在芯片面下的变化非常大。过大的曲翘导致NCO(noncontacted opening 虚焊)和SBB(solder ball bridging 桥接)这两类最为常见的缺陷。基于回流焊的复杂多芯片键合的良品率可能非常的低,使得回流焊不再是最合适的键合方式。回流焊芯片键合的良品率跟诸多因素有关,常见的有芯片大小和厚度,bump间距(pitch),基板的厚度,热膨胀系数(CTE)的不匹配(mismatch),如图二所示。同时bump pitch的进一步减小也进一步增加SBB的概率。另外值得指出的是,即使没有发生NCO和SBB缺陷,过大的chip gap height变化和过大的曲翘对下游的封装步骤也带来了巨大的挑战。

图一:常见的回流焊芯片键合流程

图二:常见的回流焊芯片键合的良品率和芯片大小和厚度的关系

我们将在下一篇深入讨论热压键合的细节及发展方向。敬请关注公众号。欢迎访问艾邦半导体网:www.ab-sm.com。

Reference

[1]3D Microelectronic Packaging, From Architectures to Applications, Springer

[2]A. Eitan, K.Hung, in Conference Proceedings from the 65th Electronic Components and

Technology Conference (ECTC) (2015)

[3] Die Attach Equipment Market Report 2019 Market and Technology Yole Report

[4]S. Lau, Thermo-compression bonding for fine-pitch copper pillar flip chip interconnect, in SEMICON Advanced Packaging Symposium

[5]J.L. Aw, et al. Thermal compression bonding with non-conductive adhesive of 30 um pitch Cu pillar micro bumps on organic substrate with bare Cu bondpads, in 2014 IEEE 16th Electronics Packaging Technology Conference (EPTC) (2014)

[6] S. Lee, Fundamentals of thermal compression bonding technology and process materials for 2.5/3D packages. 57, 157–203 (2017)

原文始发于微信公众号(艾邦半导体网):先进封装芯片键合之热压键合介绍(1)