在前篇文章(半导体封装的作用、工艺和演变)中,我们主要了解到半导体封装的作用。这些封装的形状和尺寸各异,保护和连接脆弱集成电路的方法也各不相同。在这篇文章中,我们将带您了解半导体封装的不同分类,包括制造半导体封装所用材料的类型、半导体封装的独特制造工艺,以及半导体封装的应用案例。半导体封装的分类

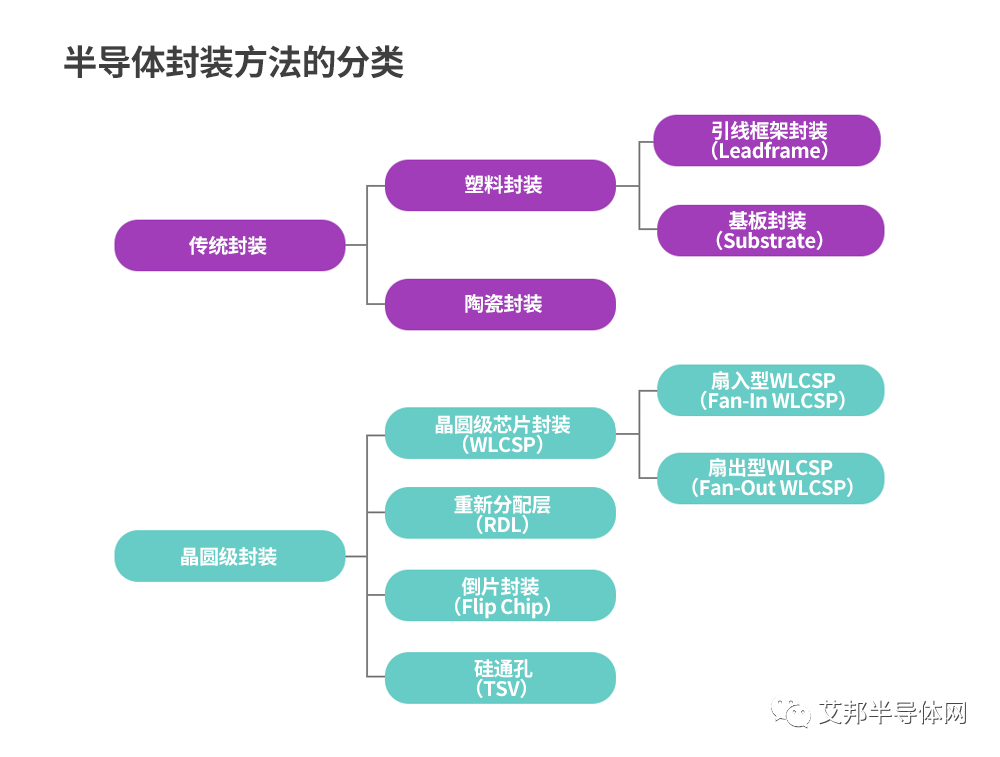

图1为半导体封装方法的不同分类,大致可以分为两种:传统封装和晶圆级(Wafer-Level)封装。传统封装首先将晶圆切割成芯片,然后对芯片进行封装;而晶圆级封装则是先在晶圆上进行部分或全部封装,之后再将其切割成单件。图1:半导体封装方法的分类(ⓒ HANOL出版社)根据封装材料的不同,传统封装方法可进一步细分为陶瓷封装和塑料封装。根据封装媒介的不同,塑料封装又可进一步分为引线框架封装(Leadframe)或基板封装(Substrate)。1)晶圆级芯片封装(WLCSP),可直接在晶圆顶部形成导线和锡球(Solder Balls),无需基板;2)重新分配层(RDL),使用晶圆级工艺重新排列芯片上的焊盘位置1,焊盘与外部采取电气连接方式;3)倒片(Flip Chip)封装,在晶圆上形成焊接凸点2进而完成封装工艺;4)硅通孔(TSV)封装,通过硅通孔技术,在堆叠芯片内部实现内部连接。晶圆级芯片封装分为扇入型WLCSP和扇出型WLCSP。扇入型WLCSP工艺将导线和锡球固定在晶圆顶部,而扇出型WLCSP则将芯片重新排列为模塑3晶圆。这样做是为了通过晶圆级工艺形成布线层,并将锡球固定在比芯片尺寸更大的封装上。1焊盘 (Pad):一种以电气方式连接至其他媒介的通道。在芯片上,焊盘通过导线或倒片凸点与外部实现电气连接;在基板上,焊盘用于芯片之间的连接。

2焊接凸点 (Solder bump):一种通过倒片键合将芯片连接到基板的导电凸点。它还可以将球栅阵列(BGA)或芯片尺寸封装(CSP)连接至电路板。

3模塑 (Molding):使用环氧树脂模塑料(EMC)密封引线键合结构或倒装芯片键合结构半导体产品的过程。塑料封装:引线框架

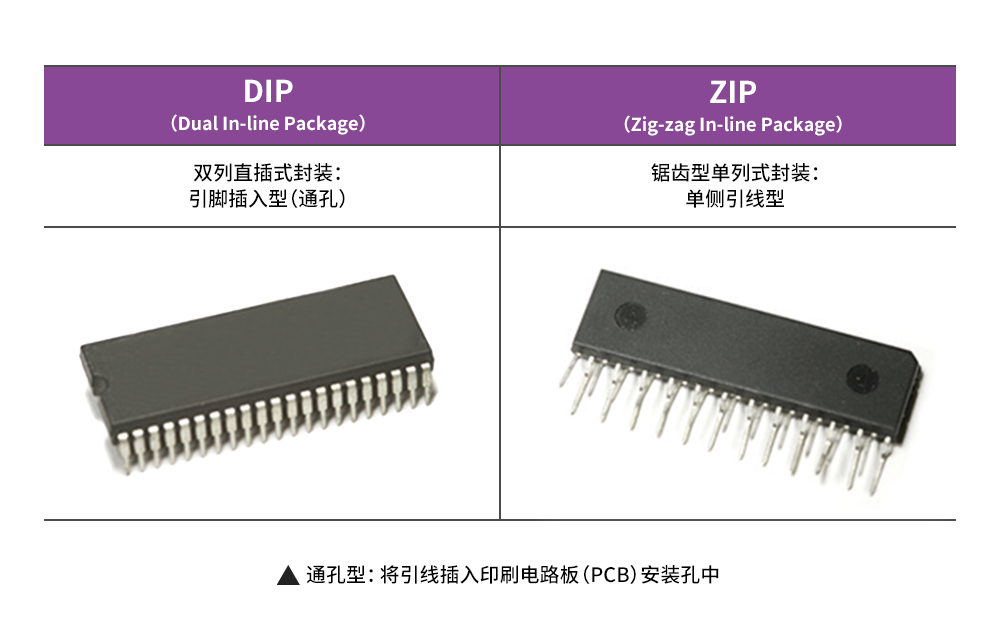

图2:引线框架封装方法的分类( ⓒ HANOL出版社 )在塑料封装方法中,芯片被环氧树脂模塑料(EMC)4等塑料材料覆盖。引线框架封装是一种塑料封装方法,采用一种被称为引线框架的金属引线作为基板。引线框架采用刻蚀工艺在薄金属板上形成布线。4环氧树脂模塑料(EMC):一种热固性塑料,具有优异的机械、电绝缘和耐温特性。环氧树脂模塑料是一种分子量相对较低的树脂,能够在固化剂或催化剂的作用下进行三维固化。图2呈现了引线框架封装方法的各种分类。20世纪70年代,人们通常采用双列直插式封装(DIP)或锯齿型单列式封装(ZIP)等通孔型技术,即,将引线插入到印刷电路板(PCB)的安装孔中。后来,随着引脚(Pin)数量的不断增加,以及PCB设计的日趋复杂,引线插孔技术的局限性也日益凸显。在此背景下,薄型小尺寸封装(TSOP)、四方扁平封装(QFP)和J形引线小外形封装(SOJ)等表面贴装型技术陆续问世。对于需要大量输入/输出(I/O)引脚(如逻辑芯片)的产品而言,可采用四方扁平封装(QFP)等封装技术,将引线固定在四个边上。为了满足系统环境对薄型化封装的需求,薄型四方扁平封装(TQFP)和薄型小尺寸封装也应运而生。随着半导体产品向更高速度迈进,支持多层布线的基板封装方法成为主流封装技术。但是,TSOP封装等引线框架封装方法因其制造成本较低,仍然得到广泛使用。引线框架通过在金属板上冲压或刻蚀布线形状制成,而基板的制造工艺则相对复杂,因此,引线框架的制造成本比基板的制造成本更低。综上,在生产不追求高速电气特性的半导体产品时,引线框架封装方法仍然是一种理想选择。塑料封装:基板封装

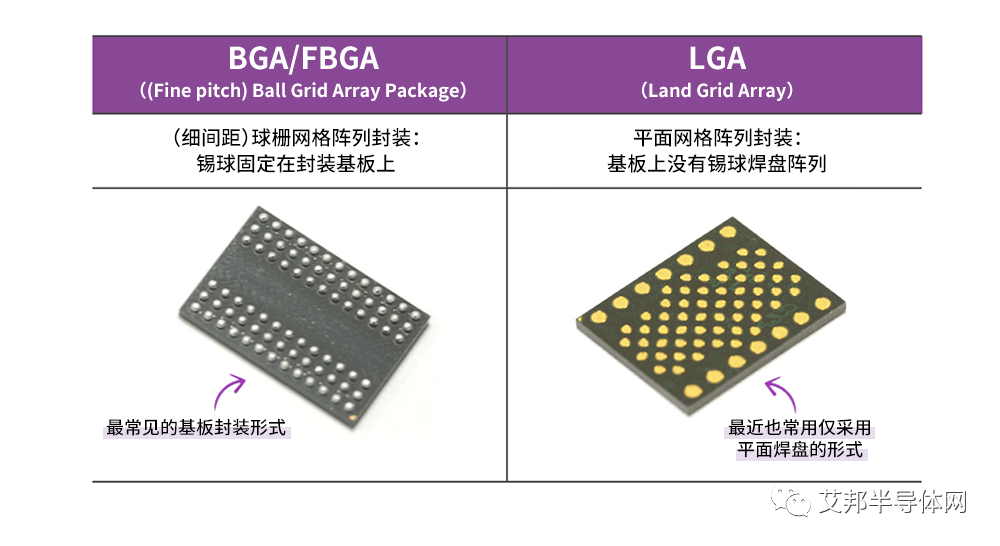

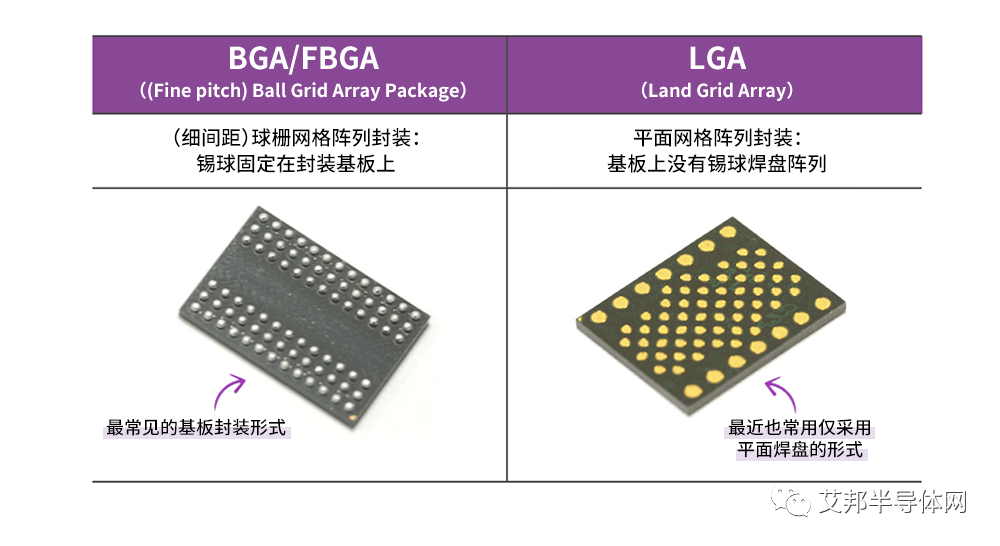

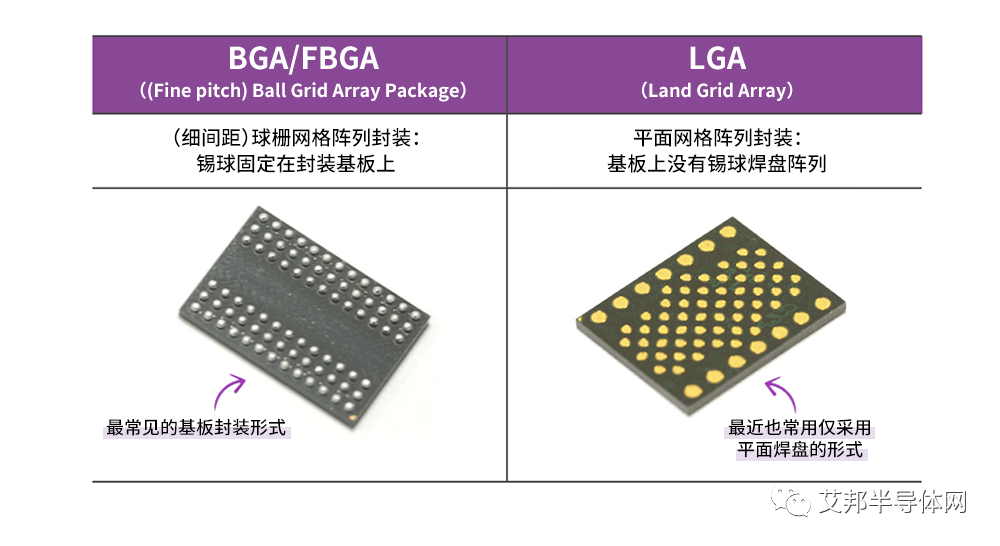

顾名思义,基板封装方法使用基板作为媒介。由于基板使用多层薄膜制成,因而基板封装有时也被称为压层式封装。不同于引线框架封装只有一个金属布线层(因为引线框架这种金属板无法形成两个以上金属层),基板封装可以形成若干布线层,因此电气特性更加优越且封装尺寸更小。引线框架封装和基板封装的另一个主要区别是布线连接工艺。连接芯片和系统的布线必须分别在引线框架和基板上实现。当需要交叉布线时,基板封装可将导线交叉部署至另一个金属层;引线框架封装由于只有一个金属层,因而无法进行交叉布线。如图3所示,基板封装可以将锡球全部排列在一个面作为引脚,由此获得大量引脚。相比之下,引线框架封装采用引线作为引脚,而引线只能在一侧的边缘形成。这样的部署也改善了基板封装的电气特性。在封装尺寸方面,引线框架封装由主框架和侧面引线所占空间构成,因而尺寸通常较大。而基板封装的引脚位于封装底部,可有效节省空间,因而尺寸通常较小。

图3:球栅阵列(BGA)和平面网格阵列(LGA)封装对比( ⓒ HANOL出版社 )鉴于上述优势,如今大多数半导体封装都采用基板封装。最常见的基板封装类型是球栅网格阵列(BGA)封装。但近年来,平面网格阵列(LGA)封装日益盛行,这种封装方法采用由扁平触点构成的网格平面结构替代锡球。陶瓷封装

陶瓷封装采用陶瓷体,具有良好的散热性和可靠性。然而,由于陶瓷制造工艺成本高昂,导致这种封装类型的总制造成本也相对较高。因此,陶瓷封装主要用于对可靠性有着极高要求的逻辑半导体,以及用于验证CMOS图像传感器(CIS)的封装。扇入型 (Fan-In) WLCSP (Wafer Level Chip Scale Package)

晶圆级芯片封装的大多数制造过程都是在晶圆上完成的,是晶圆级封装的典型代表。然而,从广义上讲,晶圆级封装还包括在晶圆上完成部分工艺的封装,例如,使用重新分配层、倒片技术和硅通孔技术的封装。在扇入型WLCSP和扇出型WLCSP中,“扇”是指芯片尺寸。扇入型WLCSP的封装布线、绝缘层和锡球直接位于晶圆顶部。与传统封装方法相比,扇入型WLCSP既有优点,也有缺点。在扇入型WLCSP中,封装尺寸与芯片尺寸相同,都可以将尺寸缩至最小。此外,扇入型WLCSP的锡球直接固定在芯片上,无需基板等媒介,电气传输路径相对较短,因而电气特性得到改善。而且,扇入型WLCSP无需基板和导线等封装材料,工艺成本较低。这种封装工艺在晶圆上一次性完成,因而在裸片(Net Die,晶圆上的芯片)数量多且生产效率高的情况下,可进一步节约成本。扇入型WLCSP的缺点在于,因其采用硅(Si)芯片作为封装外壳,物理和化学防护性能较弱。正是由于这个原因,这些封装的热膨胀系数与其待固定的PCB基板的热膨胀系数5存在很大差异。受此影响,连接封装与PCB基板的锡球会承受更大的应力,进而削弱焊点可靠性6。5热膨胀系数 (Coefficient of thermal expansion):在压力恒定的情况下,物体的体积随着温度升高而增大的比率。膨胀或收缩的程度与温度的升高或降低呈线性关系。

6焊点可靠性 (Solder joint reliability):通过焊接方式将封装与PCB连接时,确保焊点的质量足以在封装生命周期内完成预期的机械和电气连接目的。存储器半导体采用新技术推出同一容量的芯片时,芯片尺寸会产生变化,扇入型WLCSP的另一个缺点就无法使用现有基础设施进行封装测试。此外,如果封装锡球的陈列尺寸大于芯片尺寸,封装将无法满足锡球的布局要求,也就无法进行封装。而且,如果晶圆上的芯片数量较少且生产良率较低,则扇入型WLCSP的封装成本要高于传统封装。扇出型WLCSP

扇出型WLCSP既保留了扇入型WLCSP的优点,又克服了其缺点。图4显示了扇入型WLCSP和扇出型WLCSP的对比。

图4:扇入型WLCSP和扇出型WLCSP的对比(ⓒ HANOL出版社 )扇入型WLCSP的所有封装锡球都位于芯片表面,而扇出型WLCSP的封装锡球可以延伸至芯片以外。在扇入型WLCSP中,晶圆切割要等到封装工序完成后进行。因此,芯片尺寸必须与封装尺寸相同,且锡球必须位于芯片尺寸范围内。在扇出型WLCSP中,芯片先切割再封装,切割好的芯片排列在载体上,重塑成晶圆。在此过程中,芯片与芯片之间的空间将被填充环氧树脂模塑料,以形成晶圆。然后,这些晶圆将从载体中取出,进行晶圆级处理,并被切割成扇出型WLCSP单元。除了具备扇入型WLCSP的良好电气特性外,扇出型WLCSP还克服了扇入型WLCSP的一些缺点。这其中包括:无法使用现有基础设施进行封装测试;封装锡球陈列尺寸大于芯片尺寸导致无法进行封装;以及因封装不良芯片导致加工成本增加等问题。得益于上述优势,扇出型WLCSP在近年来的应用范围越来越广泛。重新分配层 (ReDistribution Layer, RDL)

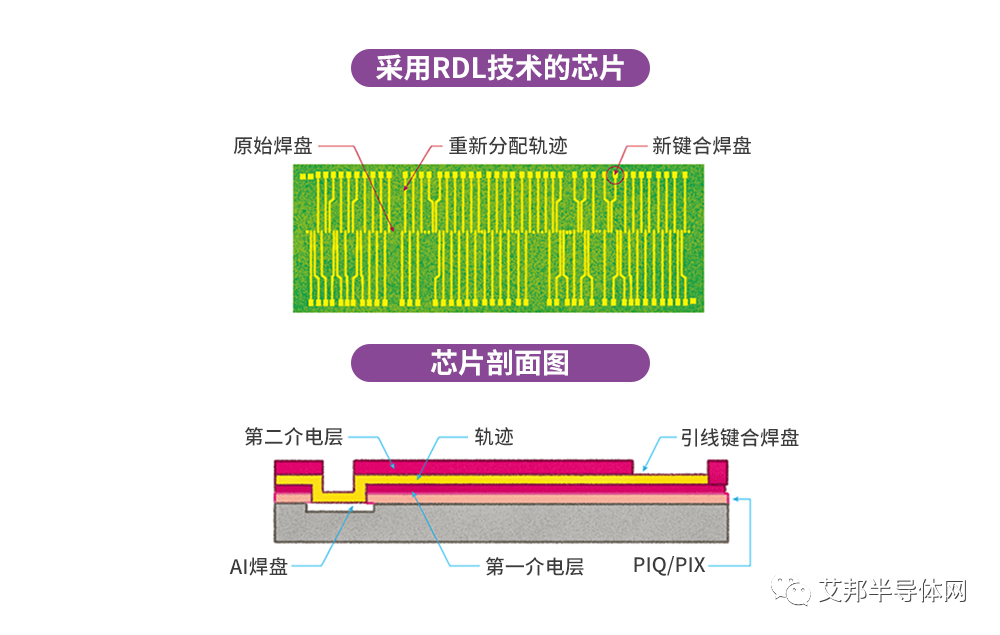

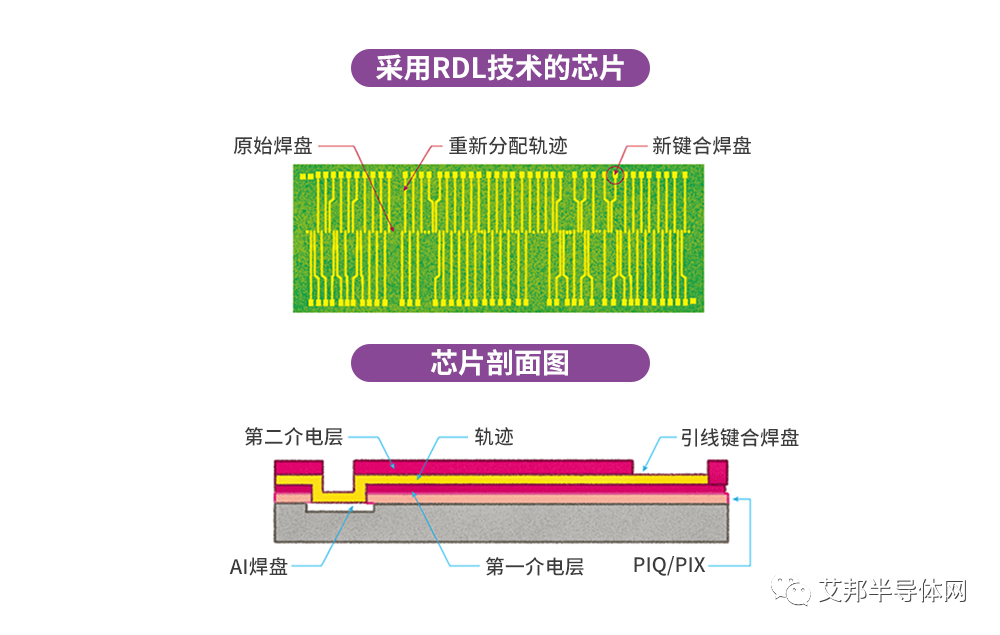

RDL技术指重新布线的行为。RDL技术旨在通过添加额外的金属层,对晶圆上已经形成的键合焊盘进行重新排列。图5显示了使用RDL技术将焊盘重新分配到边缘的中心焊盘芯片示意图和剖面图。RDL技术是一种晶圆级工艺,仅用于重新配置焊盘,经过RDL技术处理的晶圆需采用传统封装工艺完成封装。

图5:采用RDL技术的芯片与剖面图(ⓒ HANOL出版社 )如果客户想要以独特的方式排列晶圆上的焊盘,那么,相较于引入新的晶圆制造工艺,在封装过程中采用RDL技术重新排列现有晶圆上的焊盘更加高效。此外,RDL技术也可以用于中心焊盘芯片的芯片堆叠。倒片封装 (Flip Chip)

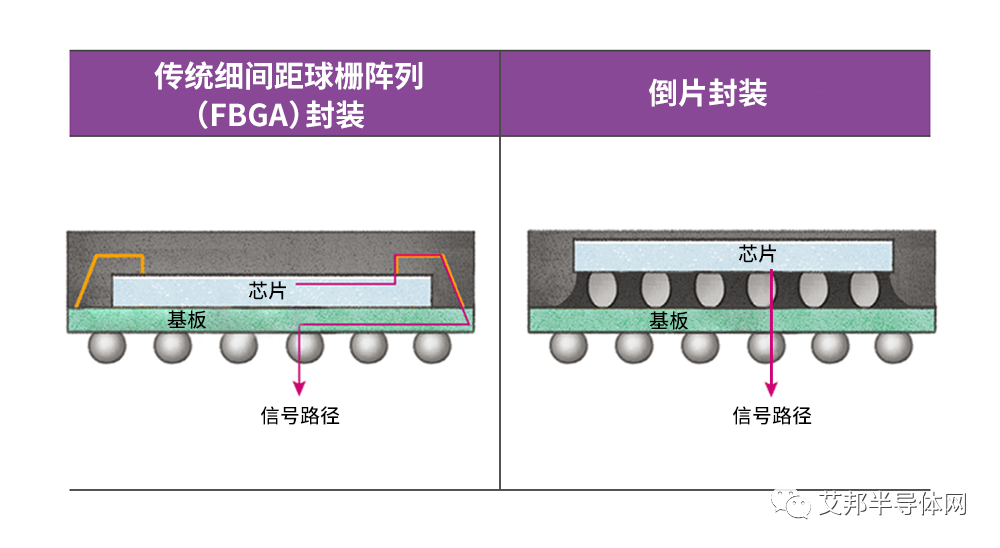

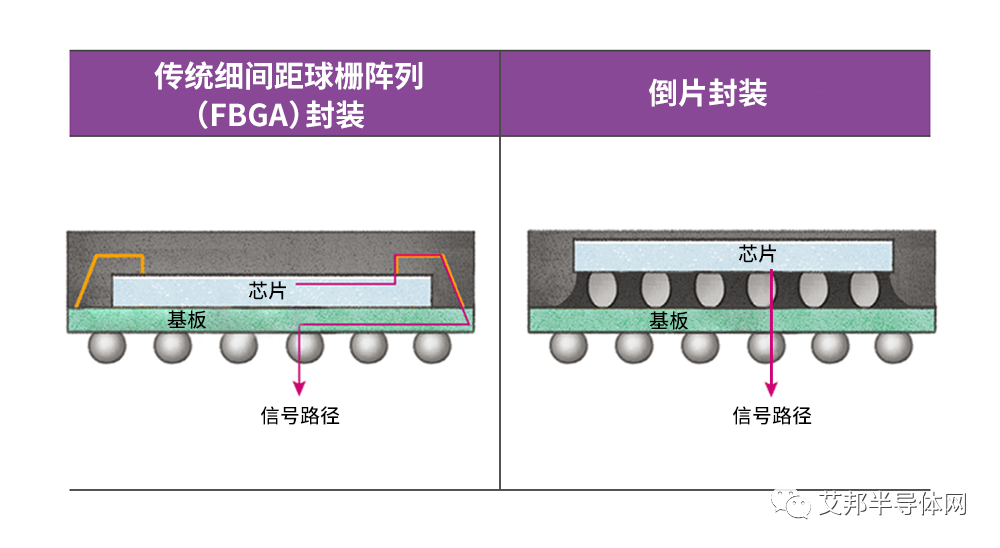

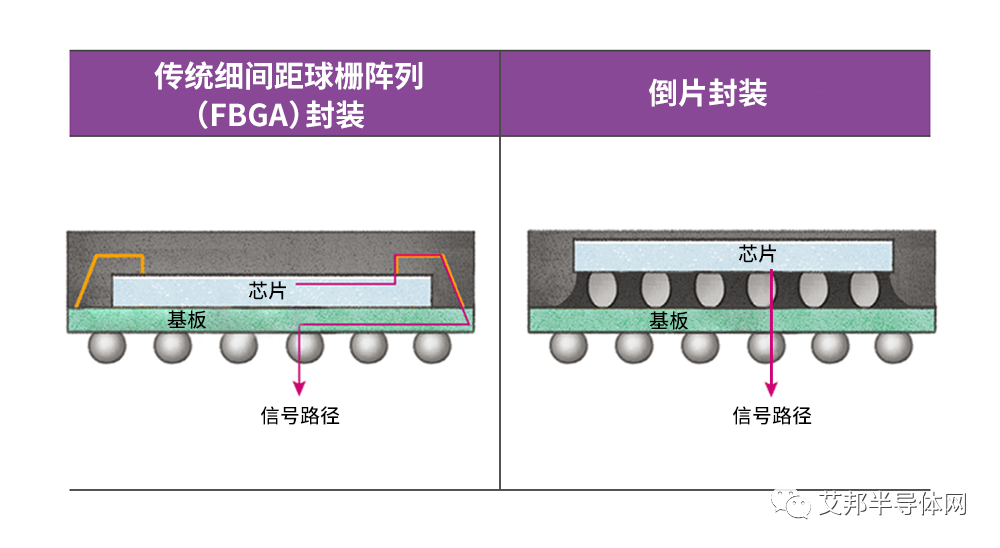

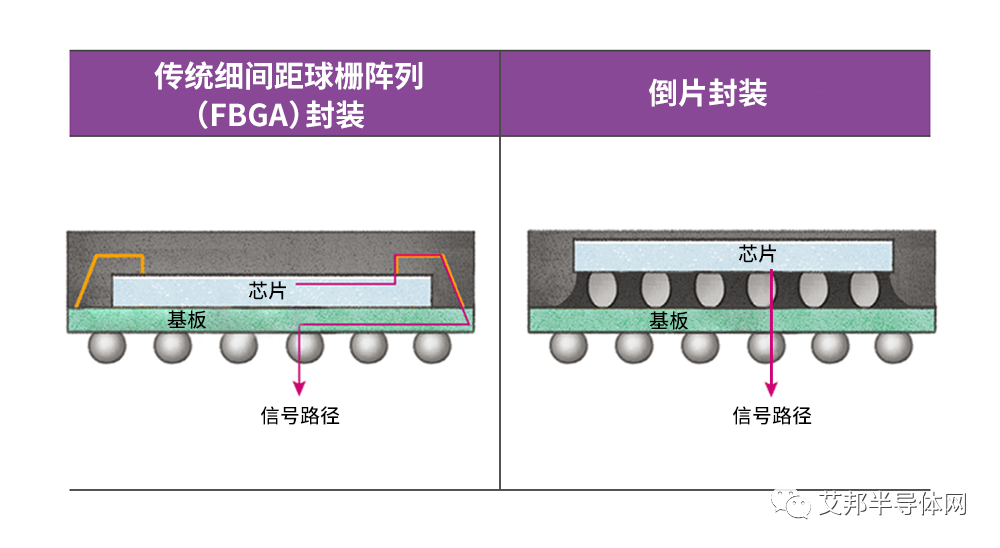

倒片封装技术因其将芯片上的凸点翻转并安装于基板等封装体上而得名。与传统引线键合一样,倒片封装技术是一种实现芯片与板(如基板)电气连接的互连技术。然而,倒片封装技术凭借其优越的电气性能,已经在很大程度上取代了引线键合。这其中有两方面的原因:一是引线键合对于可进行电气连接的输入/输出(I/O)引脚的数量和位置有限制,而倒片封装不存在这方面的限制;二是倒片封装的电信号传输路径短于引线键合。在引线键合方法中,金属焊盘在芯片表面采用一维方式排列,因此无法出现在芯片边缘或中心位置。而倒片键合方法在键合至基板或形成焊接凸点的过程中不存在任何工艺方面的限制。因此,在倒片封装方法中,金属焊盘可以采用二维方式全部排列在芯片的一个侧面,将金属焊盘的数量增加了2的次方。此外,用于形成凸点的焊盘可以布置在芯片顶部的任何位置。同时,用于供电的焊盘可以布置在靠近需要供电的区域,以进一步提升电气性能。如图6所示,在将信息从芯片导出至同一封装球时,倒片键合的信号路径要比引线键合短得多,电气性能也由此得到进一步改善。

图6:引线键合与倒片键合的信号传输路径对比(ⓒ HANOL出版社 )如前所述,WLCSP和倒片封装均可以在晶圆顶部形成锡球。尽管两种技术都可以直接安装在PCB板上,但两者之间在锡球大小方面却存在根本区别。WLCSP封装中的锡球直径通常为几百微米(μm),而倒片封装技术形成的锡球直径仅为几十微米(μm)。由于尺寸较小,我们通常将倒片封装技术形成的锡球称为“焊接凸点”,而仅仅依靠这些凸点很难保障焊点可靠性。WLCSP封装技术形成的锡球能够处理基板和芯片之间热膨胀系数差异所产生的应力,但倒片封装技术形成的焊接凸点却无法做到这一点。因此,为了确保焊点可靠性,必须使用聚合物型底部填充材料填充倒片凸点之间的空间。底部填充材料可以分散凸点所承担的应力,由此确保焊点可靠性。除了以上所述的封装技术之外,还有许多不同的半导体封装类型。原文链接:https://news.skhynix.com.cn/semiconductor-back-end-process-episode-3-understanding-the-different-types-of-semiconductor-packages/原文始发于微信公众号(艾邦半导体网):半导体封装技术的分类及制造工艺