SiC MOSFET有两种主流技术路线:平面栅和沟槽栅。平面栅更容易实现,沟槽栅则需要更高深的工艺知识。沟槽栅是垂直式SiC-SiO2界面,缺陷率更低,沟道电阻小,在较低栅氧的电场下运行沟槽型器件,仍能得到非常好的性能和较好的氧化层可靠性,这也是英飞凌选择沟槽栅的重要原因之一。

碳化硅功率半导体的性能潜力众所周知,且得到从光伏到电动汽车充电,乃至电动汽车驱动等各种应用的证明。然而,从当前高功率碳化硅MOSFET来看,仍存在一个难题:如何选择一种能平衡性能、鲁棒性、可靠性和易用性的设计。

source:英飞凌

先进设计项目着眼于面积比导通电阻,将其视为任一技术的基准参数。但其他方面性能也是成功的功率半导体器件重要标准,例如足够的可靠性。对于不同的应用,这一平衡可能略有差异,因此,合理的器件定义应当保证设计灵活性,以满足不同的任务需求,无需大量设计工作和设计布局变化。

首先,沟槽栅型的优点为可持续的长期路线图开拓了道路。历史表明,几乎所有现代碳基器件都是沟槽栅型,且已经取代了平面栅型MOSFET,碳化硅业界因此正慢慢从平面栅型向沟槽栅型架构转变。另外一个重要原因是垂直式SiC Si0₂界面的电气性能更好,这不仅仅是性能特征,也会对可靠性产生积极影响。

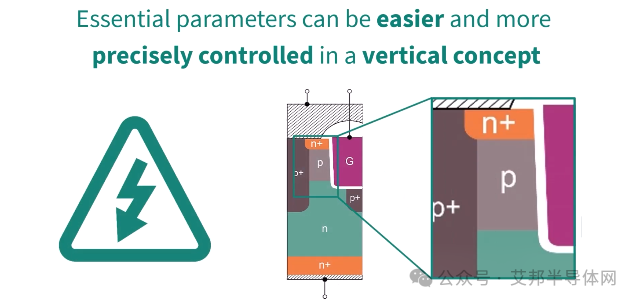

在碳化硅 MOSFET中,栅极氧化层可靠性和宇宙射线故障率,共同决定了破坏性应用中故障的FIT率。此外,决定任一技术阈值电压变化等的重要参数,如沟道尺寸和掺杂,都能在垂直结构中更容易、更准确地控制。

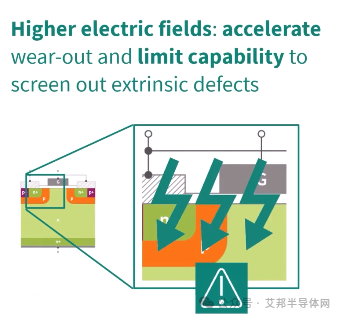

再看栅极氧化层界面质量与可靠性之间的关系,与碳基器件不同的是,碳化硅器件栅极氧化层故障会影响破坏性应用中故障的FIT率。因为碳化硅和栅极氧化层之间的界面质量仍存在多种缺陷,导致高沟道电阻。为降低这一沟道电阻,也为了发挥碳化硅的更好的性能,器件开通时,栅极氧化层上的电场会升高,不幸的是,运行中电场较高会加速器件老化,筛选出所谓杂质缺陷的能力的限制,而这正是导致最终FIT率的主要原因。

但与平面栅型相比,沟槽栅型碳化硅 MOSFET的沟道电阻要小很多。也就是说,在较低栅氧的电场下运行沟槽型器件,仍能得到非常好的性能和较好的氧化层可靠性。

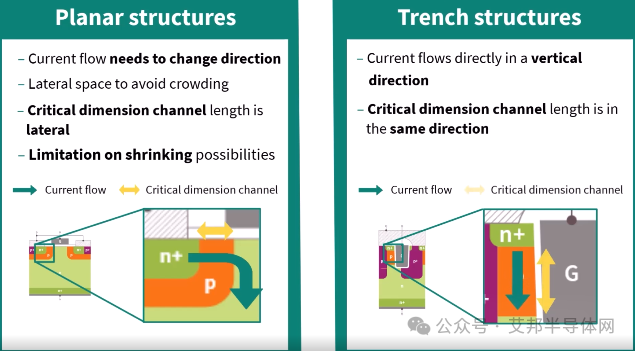

半导体行业始终有个定律——尺寸和功率密度至上。在平面栅型结构中,电流流动需要改变方向,这需要一定的横向空间来避免拥挤。另外,重要的尺寸沟道长度是横向的,导致电流流动存在较大的未使用空间,从而限制了减小芯片可能性。在沟槽型结构中,电流以垂直方式直接流动,因而尺寸通道长度也是同方向的,减小了单元尺寸,也就是降低面积比导通电阻,前题是开通时栅极处在相同的运行条件下。

总而言之,尽管碳化硅平面栅型结构简单,制造成本较低,却有高沟道电阻,芯片减小受限。碳化硅沟槽型结构沟道电阻低,芯片减小的潜力大于平面栅型结构,但是沟槽型的工艺需要高深的专业知识,并且需要氧化层角落保护。

来源:英飞凌官微

原文始发于微信公众号(艾邦半导体网):沟槽栅SiC MOS如何平衡导通电阻与可靠性